芯来科技发明多处理器中断处理装置提高SoC精确分发能力

【嘉勤点评】芯来科技发明的应用于系统级芯片中的中断处理装置,这种中断处理装置能够通过轮询仲裁机制和占有信息将中断信号发送至目标处理器核,进而实现了中断信号精确分发至对应的处理器核。

集微网消息,近日,芯来科技助力道生物联发布基于RISC-V内核的TurMass™标准无线终端SoC芯片—TK8610,该芯片产品采用芯来科技RISC-V N200系列处理器内核。

随着芯片的可集成度越来越高,芯片的算力成为了衡量一个SoC(系统级芯片)系统最重要的指标之一,因此CPU正式步入了多核时代。同时,芯片上所集成的知识产权(IP)也越来越复杂。

一般而言,IP送出的中断数量与IP的复杂程度成正比。这种情况下,片上中断和CPU多核之间的精确分发,便成为了高性能SoC设计中必须要解决的问题。

为此,芯来科技在2021年12月3日申请了一项名为“一种中断处理装置、芯片和电子设备”的发明专利(申请号:202111460925.0),申请人为芯来科技(武汉)有限公司。

在该专利中,发明了一种应用于系统级芯片中的中断处理装置,根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

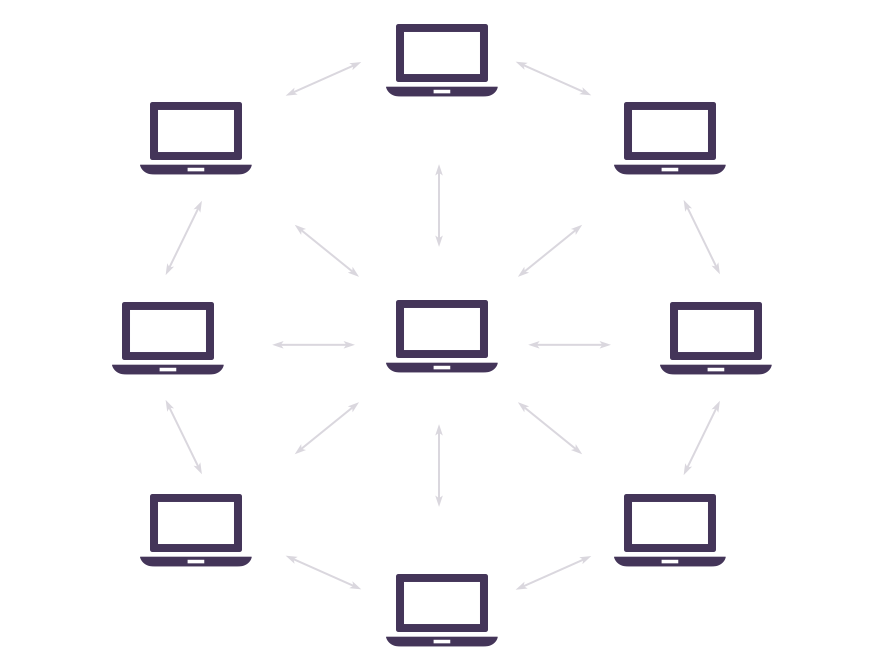

如上图,为该专利中发明的芯片的结构示意图,该芯片包括有:中断源200、多个处理器核300和中断处理装置100,中断处理装置与中断源分别和多个处理器核300均通信连接。中断处理装置用于接收多个处理器核发送的占有信息,其中还用于从多个处理器核中选择最先通过轮询仲裁机制的处理器核为目标处理器核。

此外,中断处理装置还可以在满足配置条件下,依据目标处理器核的占有信息将中断源发送的中断信号分发至目标处理器核。其中,中断机制为处理器核在顺序执行程序指令流的过程中突然被别的请求打断而中止当前的程序,转而去处理别的事情。待其处理完了别的事情,然后重新回到之前程序中断的点继续执行之前的程序指令流。

在该方案的系统中,由于有多个处理核,因此这些处理器核都会向中断处理装置发送占有信息。中断处理装置会从多个处理器核中选择最先向其发送占有信息的处理器核,或者优先级最高的处理器核为目标处理器核,且只响应目标处理器核的占有信息。

如上图,为这种芯片中断处理装置的内部结构示意图,该装置主要包括寄存器配置总线120、分发寄存器130、屏蔽寄存器140和中断分发处理模块110。这些器件均与处理器核之间通信连接,并且中断分发处理模块、屏蔽寄存器、分发寄存器、处理器核也都与中断源通信连接。

分发寄存器的数量、屏蔽寄存器的数量与中断源产生的中断信号类型数量相同,分发寄存器和屏蔽寄存器分别与中断源产生的中断信号类型一一对应设置。例如,若芯片具有m个处理器核,中断源产生n个中断信号。则应该设置n个分发寄存器和n个屏蔽寄存器,且中断信号0与分发寄存器0和屏蔽寄存器0对应设置,中断信号1与分发寄存器1和屏蔽寄存器1对应设置。

最后,如上图,为这种中断分发处理模块的电路示意图,中断分发处理模块主要由中断分发处理单元111构成,中断分发处理单元的数量为处理器核的数量与中断源产生的中断信号的数量的乘积。

此外,可以看到,每个中断分发处理单元均包括处理电路112和选择电路113,处理电路、寄存器配置总线、屏蔽寄存器和选择电路均通信连接。处理电路包括或门U1、第一与门U2和触发器D1,或门的第一输入端与触发器的输出端电连接,第二输入端与寄存器配置总线和触发器D1的数据端均电连接。

以上就是芯来科技发明的应用于系统级芯片中的中断处理装置,这种中断处理装置能够通过轮询仲裁机制和占有信息将中断信号发送至目标处理器核,进而实现了中断信号精确分发至对应的处理器核。

- 免责声明

- 世链财经作为开放的信息发布平台,所有资讯仅代表作者个人观点,与世链财经无关。如文章、图片、音频或视频出现侵权、违规及其他不当言论,请提供相关材料,发送到:2785592653@qq.com。

- 风险提示:本站所提供的资讯不代表任何投资暗示。投资有风险,入市须谨慎。

- 世链粉丝群:提供最新热点新闻,空投糖果、红包等福利,微信:msy2134。

手机中国联盟官博

手机中国联盟官博